Introduction of Interrupts

New Software programmers often get confused with the concept of interrupts. It is very simple to understand if we consider an analogy with our daily tasks. Assume you are cooking food and you get a phone call. What do you do in such situation? You first check who is calling?

- If the caller is not important then you just ignore the call and continue cooking.

- If caller is important; then you stop cooking. Probably you switch off the cooking stove. Then you answer the call. Once you finish talking, you again resume back to cooking routine.

This is exactly how interrupts work in embedded systems.

Interrupts are signals to processor that indicate an asynchronous event. Interrupts can be initiated by external peripheral devices or internally in the CPU. Broadly interrupts can be categorized in to 5 different types based on how they are generated.

- Events occuring on peripheral device

- Involuntary events internal to CPU

- Voluntary events inside CPU

- Actions by operator

- Timer interrupts

- Events occurring on peripheral devices

These interrupts are generated to notify CPU of some events occurred on connected devices. For example, RTC tick after every second or external ADC signal indicating that ADC conversion is complete.

Such external interrupts can be used for scheduling specific tasks in operating system.

- Involuntary events internal to CPU

These interrupts are generated internally to handle some error conditions or exceptions such as divide by zero or accessing memory location which are not available. Such exceptions are handled through branching in microcode. A carefully written code shall handle such exceptions to make the system fault tolerant.

- Voluntary events inside CPU

Sometimes flow of program needs to be modified so that control can go from application to OS or to supervisory tasks. Such transitions can be handled through purposefully generated interrupts such as SVC (supervisory call) or software interrupts.

- Actions by operator

Such interrupts are used to detect asynchronous actions triggered by operators such as key press. Sometimes actions are triggered by non-human operators such as temperature increase by engine, or mechanical movement because of external force. Interrupts can be used to identify such event by means of sensors. For example mechanical movement can be detected by limit switch interfaced to microcontroller. An interrupt generated on this event can be used to control actuators.

- eTimer interrupts

These interrupts are generated by internal or external timer registers. This is categorized separately because in most operating systems timer interrupts are required for task scheduling.

Internal Handling Of Interrupts

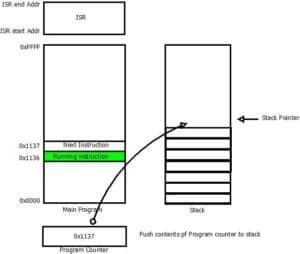

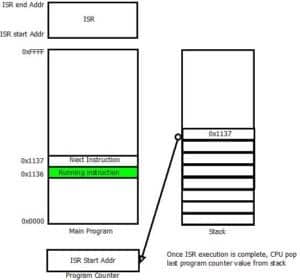

Once an interrupt signal is received, the CPU completes the instruction that is currently being executed. Then the contents of program counter are saved to interrupt return location or on stack. In many cases complete CPU state is saved so that any previous instruction information can be saved. This is done by pushing CPU flags and status register to stack. This process is often called as context saving.

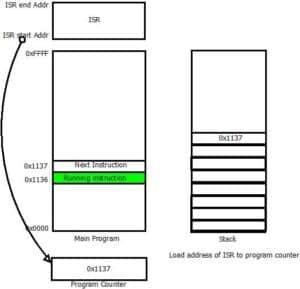

Once context is saved, program counter is loaded with memory location address of interrupt handler or ISR (interrupt service routine). Then the ISR is executed. Once the ISR execution is complete control shall return to main program. This is done by fetching the saved context back to CPU registers. This is simply done by poping the information saved on stack in reversed order.

Diagrams below explains sequence of simple interrupt handling.

Interrupt handling step 1: Interrupt is detected. CPU first complete the execution of running instruction

Interrupt handling step 2: Contents of PC, Program status register and other CPU registers pushed to stack

Interrupt handling step 3: Program counter is loaded with Interrupt Vector (address of ISR)

Interrupt handling step 4: Execution of ISR started

Interrupt handling step 5: Execution of ISR complete.

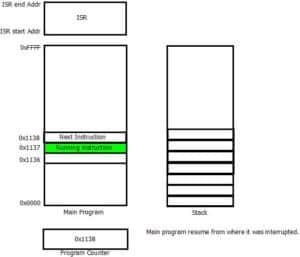

Content loaded on stack are poped in reverse order. Program counter is loaded with address of next instruction.

Interrupt handling step 6: Main program execution resume back.

Modern microprocessors and microcontrollers provide way to handle multiple interrupts. In some microcontrollers, interrupts have fixed priority whereas most of the modern architectures provide configuration options to change interrupt priorities.

CPU provides instructions to enable and disable all interrupts globally. Individual interrupts also can be enabled or disabled using interrupt control registers. Once an interrupt is generated other interrupts are disabled. If any other interrupt is active then its state is stored so that it can be serviced once first ISR execution is complete. Some architecture even supports nested interrupts. A higher priority interrupt can stop lower priority ISR. Then program counter and other CPU status registers are saved to stack and program counter is loaded with address of higher priority interrupt vector. Once the higher priority ISR is execution is complete the saved content are reloaded and previous low priority ISR continues.